#### **SECTION 9**

### **ELECTRICAL SPECIFICATIONS**

### 9.1 INTRODUCTION

This section contains the electrical specifications and associated timing information for the MC68HC05E0.

## 9.2 MAXIMUM RATINGS <sup>†</sup>

Table 9-1. Maximum ratings

| Rating                                                                                                   | Symbol           | Value                                             | Unit           |

|----------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------|----------------|

| Supply Voltage                                                                                           | V <sub>DD</sub>  | - 0.3 to 7.0                                      | V              |

| Input Voltage                                                                                            | Vin              | V <sub>SS</sub> - 0.3 to<br>V <sub>DD</sub> + 0.3 | V              |

| Operating Temperature Range                                                                              | Тд               | T <sub>L</sub> to T <sub>H</sub><br>0 to 70       | °C             |

| Storage Temperature Range                                                                                | T <sub>stg</sub> | - 65 to 150                                       | °C             |

| Current Drain per Pin * Excluding V DD and VSS VDD (total through two pins) VSS (total through two pins) | 1D               | 25<br>100<br>250                                  | mA<br>mA<br>mA |

- \* One pin at a time, observing maximum power dissipation limits.

- This device contains protective circuitry against damage due to high static voltages or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (eg. either GND or VDD).

MC68HC05E0

**ELECTRICAL SPECIFICATIONS**

MOTOROLA

9-1

# 9.3 THERMAL CHARACTERISTICS AND POWER CONSIDERATIONS

The average chip junction temperature, T<sub>J</sub>, in degrees Celsius can be obtained from the following equation:

$$T_{J} = T_{A} + (P_{D} \bullet \theta_{JA})$$

Where:

$T_A$  = Ambient temperature ( ${}^{\circ}$ C)

θ<sub>IA</sub> = Package thermal resistance, junction-to-ambient (OC/W)

$P_D = P_{INT} + P_{I/O}(W)$

$P_{INT}$  = Internal chip power =  $I_{DD} \cdot V_{DD}$  (W)

$P_{I/O}$  = Power dissipation on input and output pins (user determined) (W)

Note: For most applications PI/O < PINT and can be neglected.

An approximate relationship between PD and TJ (if PI/O is neglected) is:

$$P_D = K + (T_J + 273^{\circ}C)$$

Solving the equations PD and TJ for K gives:

$$K = P_D \bullet (T_A + 273^{\circ}C) + \theta_{JA} \bullet P_D^2$$

Where K is a constant pertaining to a particular part. K can be determined by measuring PD (at equilibrium) for known TA. Using this value of K, the values of PD and TJ can be obtained by solving the above equations for any value of TA. The package thermal characteristics are shown in Table 9-2.

Table 9-2. Thermal Characteristics

| Characteristics                 | Symbol          | Value | Unit |

|---------------------------------|-----------------|-------|------|

| Thermal Resistance              | θ <sub>JA</sub> |       | °C/W |

| Plastic 68-Pin Quad Pack (PLCC) |                 | 50    |      |

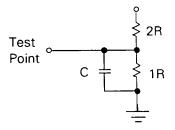

| Pins        | R1      | R2      | С     |

|-------------|---------|---------|-------|

| A12 - A0,   | 3.26 kΩ | 2.38 kΩ | 50 pF |

| PD7 - PD5,  |         |         | '     |

| CSROM, RAW, |         |         |       |

| CS2, CS3    |         |         |       |

Figure 9-1. Equivalent Test Load

MOTOROLA 9-2 **ELECTRICAL SPECIFICATIONS**

MC68HC05E0

# 9.4 DC ELECTRICAL CHARACTERISTICS

$(V_{DD} = 5.0 \text{Vdc} \pm 10\%, V_{SS} = 0 \text{Vdc}, T_A = 0 \text{ to } 70^{\circ}\text{C})$

Table 9-3. DC Electrical Characteristics (5V)

| Characteristic                                                                                                                                                                                | Symbol                              | Min                            | Max             | Unit                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------------------------------|-----------------|----------------------------|

| Output Voltage (all output pins)   Load = 10 μΑ   Load = -10 μΑ                                                                                                                               | VOH<br>VOF                          | -<br>VDD-0.1                   | 0.1             | V                          |

| Output Voltage (address bus and data bus)  Load = 1.6 mA  Load = -0.8 mA                                                                                                                      | Vol<br>Voh                          | -<br>V <sub>DD</sub> -1.4      | 0.4<br>-        | V                          |

| Input High Voltage                                                                                                                                                                            | VIH                                 | 0.5xV <sub>DD</sub>            | -               | V                          |

| Input Low Voltage                                                                                                                                                                             | VIL                                 | Vss                            | 0.8             | V                          |

| Supply Current (f <sub>op</sub> = 4 MHz, f <sub>osc</sub> = 8 MHz)<br>Run<br>Wait<br>Stop                                                                                                     | IDD                                 | -<br>-<br>-                    | 25<br>20<br>50  | mA<br>mA<br>μA             |

| High- Z Leakage Current (All input pins except RESET , PD5, PD6, PD7)                                                                                                                         | lıL                                 | ~                              | ±10             | μΑ                         |

| Output High Source Current (V <sub>OH</sub> = 2.4 V) Port A Port B Ports C, D, E and CSROM                                                                                                    | Іон                                 | 10<br>5<br>2.5                 | -               | mA<br>mA                   |

| Output Low Sink Current  Port A (VOL = 0.4 V)  Port A (VOL = 1.0 V)  Port B (VOL = 0.4 V)  Port B (VOL = 1.0 V)  Ports C, D, E and CSROM (VOL = 0.4 V)  Ports C, D, E and CSROM (VOL = 1.0 V) | loL                                 | 8<br>24<br>6<br>16<br>1.6<br>4 | <br>-<br>-<br>- | mA<br>mA<br>mA<br>mA<br>mA |

| Input Current RESET , PD5, PD6, PD7 INTX, OSC1                                                                                                                                                | lin                                 | -70<br>-                       | -<br>±1         | μА                         |

| Capacitance Ports (as input or output) RESET, INTX                                                                                                                                            | C <sub>out</sub><br>C <sub>in</sub> | <u>-</u><br>-                  | 12<br>8         | pF<br>pF                   |

Notes: Wait I<sub>DD</sub>: Only timer system active. If Serial Interface active add 10% to current drain.

Run  $I_{DD}$ , Wait  $I_{DD}$ : Measured using external square clock source (Fosc = 8 MHz), all inputs 0.2V from rail, no DC loads, maximum load on outputs 50pF (OSC2 load 20pF).

Wait, Stop I<sub>DD</sub>: All ports configured as inputs ,  $V_{il} = 0.2V$  and  $V_{ih} = V_{DD}$  - 0.2V.

Stop  $I_{DD}$  measured with OSC1 =  $V_{SS}$ .

Wait I<sub>DD</sub> is affected linearly by the OSC2 capacitance.

MC68HC05E0

**ELECTRICAL SPECIFICATIONS**

MOTOROLA

9-3

## 9.5 AC ELECTRICAL CHARACTERISTICS

$(V_{DD} = 5.0 \text{V dc} \pm 10\%, V_{SS} = 0 \text{Vdc}, T_{A} = 0 \text{ to } 70^{\circ}\text{C})$

Table 9-4. AC Electrical Characteristics (5V)

| Characteristic                                  | Symbol           | Min | Max | Unit             |

|-------------------------------------------------|------------------|-----|-----|------------------|

| Frequency of Operation                          |                  | ,   |     |                  |

| Crystal                                         | fosc             | -   | 8.0 | MHz              |

| External Clock                                  | f <sub>osc</sub> | dc  | 8.0 | MHz              |

| Internal Operating Frequency                    |                  |     |     |                  |

| Crystal (f <sub>osc</sub> + 2)                  | P02              | _   | 4.0 | MHz              |

| External Clock (f osc + 2)                      | P02              | dc  | 4.0 | MHz              |

| Cycle Time                                      | t <sub>cyc</sub> | 250 | _   | ns               |

| Crystal Oscillator Startup Time                 | toxov            |     | 100 | ms               |

| STOP Recovery Startup Time (Crystal Oscillator) | tILCH            |     | 100 | ms               |

| RESET Pulse Width                               | t <sub>RL</sub>  | 1.5 |     | t <sub>cyc</sub> |

| Interrupt Pulse Width Low (Edge-Triggered)      | tiLiH            | 125 | -   | ns               |

| Interrupt Pulse Period                          | tilil            | *   |     | t <sub>cyc</sub> |

| OSC1 Pulse Width                                | tOH, tOL         | 55  |     | ns               |

<sup>\*</sup> The minimum period t<sub>|L|L</sub> should not be less than the number of cycle times it takes to execute the interrupt service routine plus 21 t<sub>cyc</sub>.

MOTOROLA 9-4 **ELECTRICAL SPECIFICATIONS**

MC68HC05E0

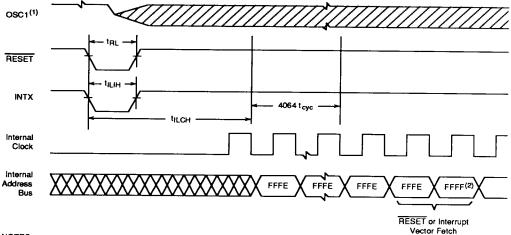

### NOTES:

- 1. Represents the internal gating of the OSC1 pin.

- 2. RESET vector address shown for timing example.

Figure 9-2. Stop Recovery Timing Diagram

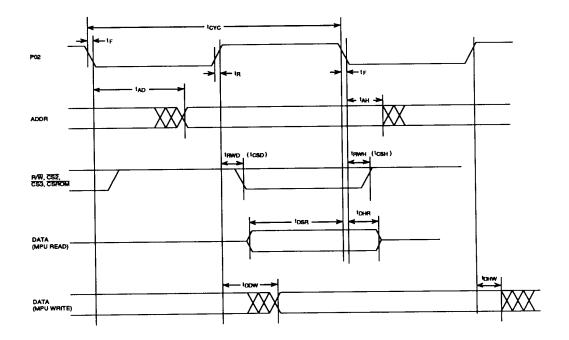

Table 9-5. Expanded Bus Timing

| Num | Characteristic         | Symbol                          | Min | Тур | Max | Unit |

|-----|------------------------|---------------------------------|-----|-----|-----|------|

| 1   | Cycle Time             | tcyc                            | 250 | _   | DC  | ns   |

| 2   | Clock Transition       | t <sub>R</sub> , t <sub>F</sub> | _   | 10  | 25  | ns   |

| 3   | Read/Write Hold        | <sup>t</sup> RWH                | 0   | _   | -   | ns   |

| 4   | Address Hold           | <sup>‡</sup> AH                 | 0   | -   | -   | ns   |

| 5   | Read/Write Delay       | <sup>†</sup> RWD                | _   | _   | 25  | ns   |

| 6   | Address Delay          | <sup>‡</sup> AD                 | _   | 40  | 75  | ns   |

| 7   | Data Set-up (MPU Read) | t <sub>DSR</sub>                | 40  | -   | -   | ns   |

| 8   | Data Hold (MPU Read)   | tDHR                            | 0   | _   | -   | ns   |

| 9   | Data Delay (MPU Write) | tDDW                            | _   | 60  | 100 | ns   |

| 10  | Data Hold (MPU Write)  | tDHW                            | 20  | _   | _   | ns   |

| 11  | Chip Select Hold       | tcsh                            | 0   | -   | -   | ns   |

| 12  | Chip Select Delay      | tcsD                            | _   | -   | 25  | ns   |

MC68HC05E0

**ELECTRICAL SPECIFICATIONS**

MOTOROLA

9-5

Figure 9-3. Expanded Bus Timing Diagram

MOTOROLA 9-6 **ELECTRICAL SPECIFICATIONS**

MC68HC05E0

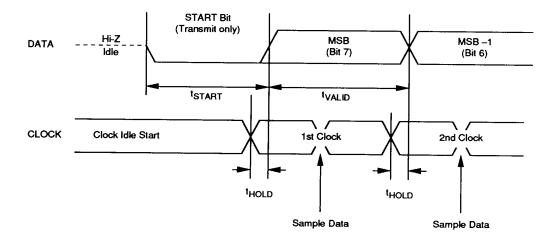

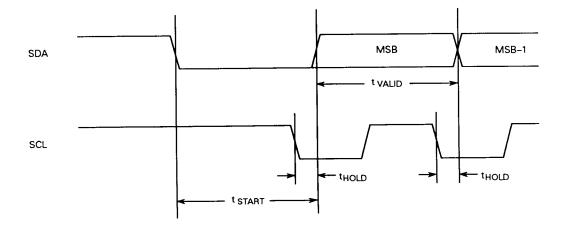

### 9.6 SERIAL INTERFACE TIMING

$t_{HOLD}$  = 1 Bus Cycle Time +  $t_{pd}$  ( $t_{pd} \approx 0 \rightarrow 30 \text{ ns}$ )  $t_{START}$  =  $t_{VALID}$  = 1/SPI Transfer Frequency (SPI Transfer Frequency determined by BD0/BD1)

Figure 9-4. SPI Timing Diagram

t<sub>HOLD</sub> = 1 Bus Cycle Time + t<sub>pd</sub>

$(t_{pd} \approx 0 \rightarrow 30 \text{ ns})$

t<sub>START</sub> = t<sub>VALID</sub> = 1 / I<sup>2</sup>C Transfer Frequency (I<sup>2</sup>C Transfer Frequency determined by BD0/BD1)

Figure 9-5. I<sup>2</sup>C-bus Timing Diagram