# Dual Single-Supply Audio Operational Amplifier

SSM2135

#### **FEATURES**

Excellent Sonic Characteristics

High Output Drive Capability

5.2 nV/√Hz Equivalent Input Noise @ 1 kHz

0.001% THD+N (V₀ = 2.5 V p-p @ 1 kHz)

3.5 MHz Gain Bandwidth

Unity-Gain Stable

Low Cost

#### **APPLICATIONS**

Multimedia Audio Systems

Microphone Preamplifier

Headphone Driver

Differential Line Receiver

Balanced Line Driver

Audio ADC Input Buffer

Audio DAC I-V Converter and Filter

Pseudo-Ground Generator

#### GENERAL DESCRIPTION

The SSM2135 Dual Audio Operational Amplifier permits excellent performance in portable or low power audio systems, with an operating supply range of +4 V to +36 V or  $\pm 2$  V to  $\pm 18$  V. The unity gain stable device has very low voltage noise of 4.7 nV/ $\sqrt{\text{Hz}}$ , and total harmonic distortion plus noise below 0.01% over normal signal levels and loads. Such characteristics are enhanced by wide output swing and load drive capability. A unique output stage\* permits output swing approaching the rail

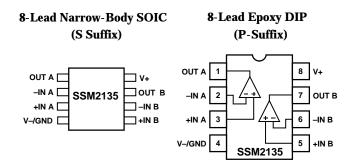

#### PIN CONNECTIONS

under moderate load conditions. Under severe loading, the SSM2135 still maintains a wide output swing with ultralow distortion.

Particularly well suited for computer audio systems and portable digital audio units, the SSM2135 can perform preamplification, headphone and speaker driving, and balanced line driving and receiving. Additionally, the device is ideal for input signal conditioning in single-supply sigma-delta analog-to-digital converter subsystems such as the AD1878/AD1879.

The SSM2135 is available in 8-lead plastic DIP and SOIC packages, and is guaranteed for operation over the extended industrial temperature range of -40°C to +85°C.

\*Protected by U. S. Patent No. 5,146,181.

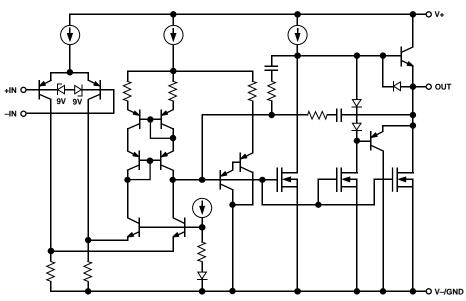

#### FUNCTIONAL BLOCK DIAGRAM

REV. D

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

$\begin{tabular}{ll} SSM2135-SPECIFICATIONS & (V_S = +5 \ V, -40 \ ^\circ C < T_A < +85 \ ^\circ C \ unless \ otherwise \ noted. \\ Typical specifications apply at T_A = +25 \ ^\circ C.) \end{tabular}$

| Parameter                                                                                                                                                                           | Symbol                                                           | Conditions                                                                                                                                                                                                                                                                                                                                                           | Min            | Тур                                        | Max                      | Units                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------------------------|--------------------------|-----------------------------------------|

| AUDIO PERFORMANCE Voltage Noise Density Current Noise Density Signal-To-Noise Ratio Headroom Total Harmonic Distortion                                                              | e <sub>n</sub> i <sub>n</sub> SNR HR THD+N                       | $\begin{array}{l} f = 1 \text{ kHz} \\ f = 1 \text{ kHz} \\ 20 \text{ Hz to } 20 \text{ kHz, } 0 \text{ dBu} = 0.775 \text{ V rms} \\ \text{Clip Point} = 1\% \text{ THD+N, } f = 1 \text{ kHz, } R_L = 10 \text{ k}\Omega \\ A_V = +1,  V_O = 1 \text{ V p-p, } f = 1 \text{ kHz, } 80 \text{ kHz LPF} \\ R_L = 10 \text{ k}\Omega \\ R_L = 32  \Omega \end{array}$ |                | 5.2<br>0.5<br>121<br>5.3<br>0.003<br>0.005 |                          | nV/√Hz<br>pA/√Hz<br>dBu<br>dBu<br>%     |

| DYNAMIC PERFORMANCE Slew Rate Gain Bandwidth Product Settling Time                                                                                                                  | SR<br>GBW<br>t <sub>S</sub>                                      | $R_L=2~k\Omega,~T_A=+25^{\circ}C$ to 0.1%, 2 V Step                                                                                                                                                                                                                                                                                                                  | 0.6            | 0.9<br>3.5<br>5.8                          |                          | V/µs<br>MHz<br>µs                       |

| INPUT CHARACTERISTICS Input Voltage Range Input Offset Voltage Input Bias Current Input Offset Current Differential Input Impedance Common-Mode Rejection Large Signal Voltage Gain | $V_{CM} \\ V_{OS} \\ I_{B} \\ I_{OS} \\ Z_{IN} \\ CMR \\ A_{VO}$ | $\begin{split} V_{OUT} &= 2 \ V \\ V_{CM} &= 0 \ V, \ V_{OUT} = 2 \ V \\ V_{CM} &= 0 \ V, \ V_{OUT} = 2 \ V \\ 0 \ V &\leq V_{CM} \leq 4 \ V, \ f = dc \\ 0.01 \ V &\leq V_{OUT} \leq 3.9 \ V, \ R_L = 600 \ \Omega \end{split}$                                                                                                                                     | 0<br>87<br>2   | 0.2<br>300<br>4<br>112                     | +4.0<br>2.0<br>750<br>50 | V<br>mV<br>nA<br>nA<br>MΩ<br>dB<br>V/μV |

| OUTPUT CHARACTERISTICS Output Voltage Swing High Output Voltage Swing Low Short Circuit Current Limit                                                                               | V <sub>OH</sub> V <sub>OL</sub> I <sub>SC</sub>                  | $R_L = 100 \text{ k}\Omega$ $R_L = 600 \Omega$ $R_L = 100 \text{ k}\Omega$ $R_L = 600 \Omega$                                                                                                                                                                                                                                                                        | 4.1 3.9        | ±30                                        | 3.5<br>3.0               | V<br>V<br>mV<br>mV<br>mA                |

| POWER SUPPLY Supply Voltage Range Power Supply Rejection Ratio Supply Current                                                                                                       | V <sub>S</sub> PSRR I <sub>SY</sub>                              | Single Supply Dual Supply $V_S = +4 \text{ V to } +6 \text{ V, } f = dc$ $V_{OUT} = 2.0 \text{ V, No Load}$ $V_S = +5 \text{ V}$ $V_S = \pm 18 \text{ V, } V_{OUT} = 0 \text{ V, No Load}$                                                                                                                                                                           | +4<br>±2<br>90 | 120<br>2.8<br>3.7                          | +36<br>±18<br>6.0<br>7.6 | V<br>V<br>dB<br>mA<br>mA                |

#### ABSOLUTE MAXIMUM RATINGS

| Supply Voltage                                             |

|------------------------------------------------------------|

| Single Supply                                              |

| Dual Supply                                                |

| Input Voltage                                              |

| Differential Input Voltage 10 V                            |

| Output Short Circuit Duration Indefinite                   |

| Storage Temperature Range65°C to +150°C                    |

| Operating Temperature Range40°C to +85°C                   |

| Junction Temperature Range $(T_J)$ 65°C to +150°C          |

| Lead Temperature (Soldering, 60 sec) $\dots +300^{\circ}C$ |

|                                                            |

#### **ESD RATINGS**

| 883 (Human Body) Model | <br>kV  |

|------------------------|---------|

| EIAJ Model             | <br>5 V |

### THERMAL CHARACTERISTICS

Thermal Resistance<sup>1</sup>

| 8-Lead Plastic DIP | $	heta_{ m JA}$ | 103°C/W |

|--------------------|-----------------|---------|

|                    | $	heta_{ m JC}$ | 43°C/W  |

| 8-Lead SOIC        | $	heta_{ m JA}$ | 158°C/W |

|                    | $	heta_{ m JC}$ | 43°C/W  |

$<sup>^1\</sup>theta_{JA}$  is specified for worst case conditions, i.e.,  $\theta_{JA}$  is specified for device in socket for P-DIP and device soldered in circuit board for SOIC package.

#### **ORDERING GUIDE**

| Temperature |                | Package            | Package |  |

|-------------|----------------|--------------------|---------|--|

| Range       |                | Description        | Option  |  |

| SSM2135P    | -40°C to +85°C | 8-Lead Plastic DIP | N-8     |  |

| SSM2135S    | -40°C to +85°C | 8-Lead SOIC        | SO-8    |  |

-2-REV. D

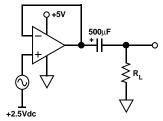

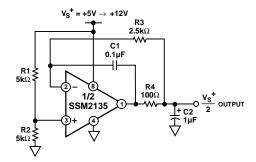

Figure 1. Test Circuit for Figures 2-4

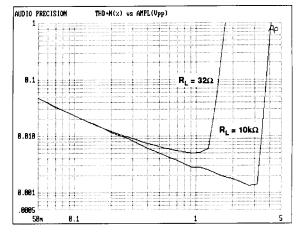

Figure 2. THD+N vs. Amplitude (See Test Circuit;  $A_V = +1$ ,  $V_S = +5$  V, f = 1 kHz, with 80 kHz Low-Pass Filter)

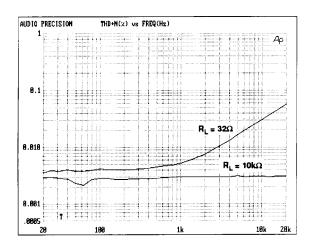

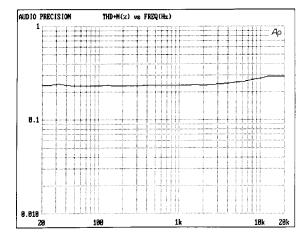

Figure 3. THD+N vs. Frequency (See Test Circuit;  $A_V = +1$ ,  $V_{IN} = 1$  V p-p, with 80 kHz Low-Pass Filter)

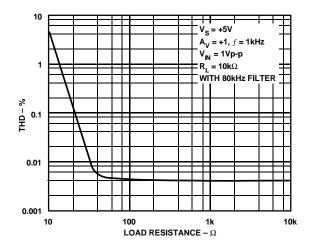

Figure 4. THD+N vs. Load (See Test Circuit)

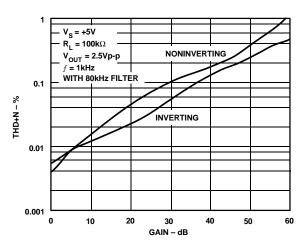

Figure 5. THD+N vs. Gain

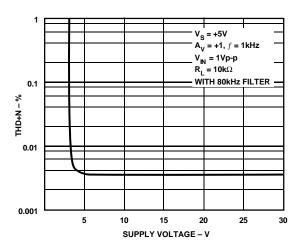

Figure 6. THD+N vs. Supply Voltage

REV. D -3-

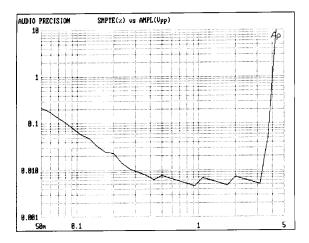

Figure 7. SMPTE Intermodulation Distortion ( $A_V = +1$ ,  $V_S = +5$  V, f = 1 kHz,  $R_L = 10$  k $\Omega$ )

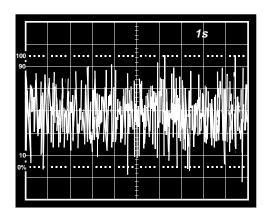

Figure 8. Input Voltage Noise (20 nV/div)

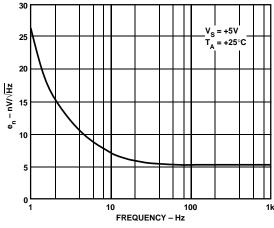

Figure 9. Voltage Noise Density vs. Frequency

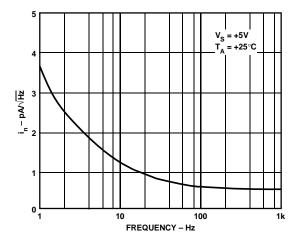

Figure 10. Current Noise Density vs. Frequency

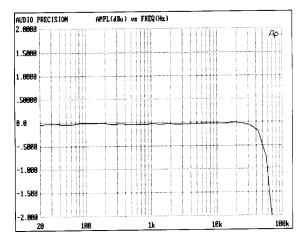

Figure 11. Frequency Response ( $A_V = +1$ ,  $V_S = +5$  V,  $V_{IN} = 1$  V p-p,  $R_L = 10$  k $\Omega$ )

Figure 12. Square Wave Response ( $V_S = +5 V$ ,  $A_V = +1$ ,  $R_L = \infty$ )

-4- REV. D

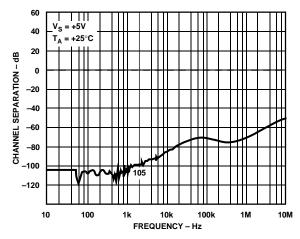

Figure 13. Crosstalk vs. Frequency ( $R_L = 10 \text{ k}\Omega$ )

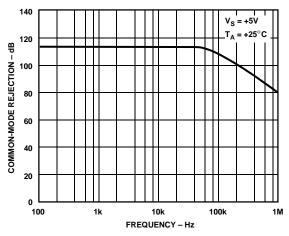

Figure 14. Common-Mode Rejection vs. Frequency

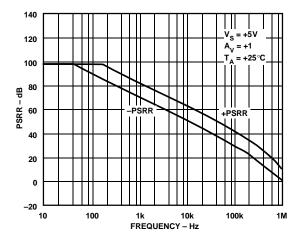

Figure 15. Power Supply Rejection vs. Frequency

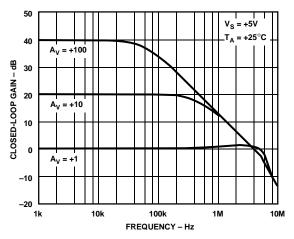

Figure 16. Closed-Loop Gain vs. Frequency

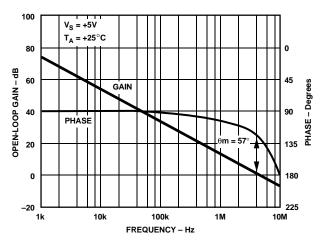

Figure 17. Open-Loop Gain and Phase vs. Frequency

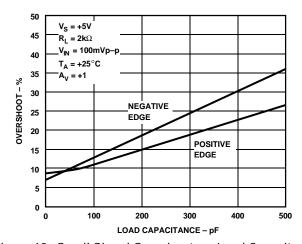

Figure 18. Small Signal Overshoot vs. Load Capacitance

REV. D \_5\_

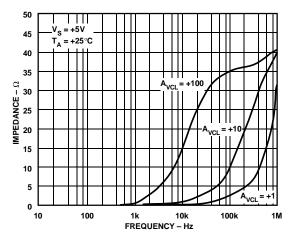

Figure 19. Output Impedance vs. Frequency

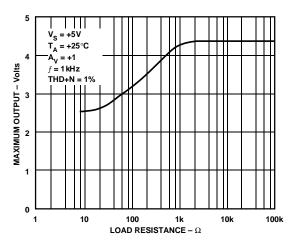

Figure 20. Maximum Output Voltage vs. Load Resistance

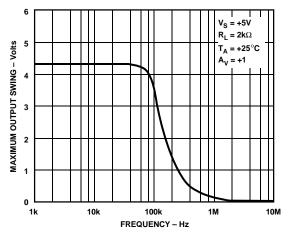

Figure 21. Maximum Output Swing vs. Frequency

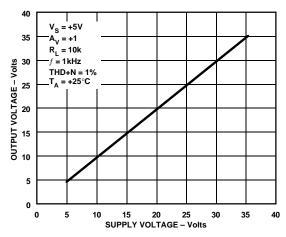

Figure 22. Output Swing vs. Supply Voltage

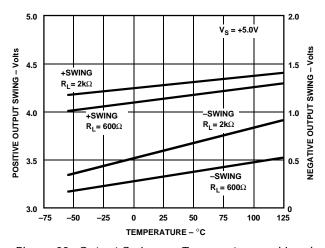

Figure 23. Output Swing vs. Temperature and Load

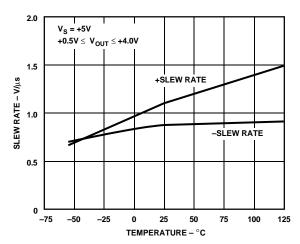

Figure 24. Slew Rate vs. Temperature

-6- REV. D

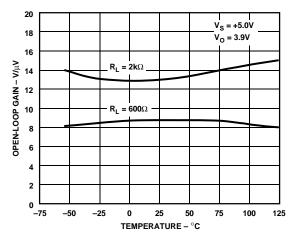

Figure 25. Open-Loop Gain vs. Temperature

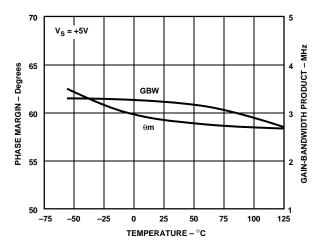

Figure 26. Gain Bandwidth Product and Phase Margin vs. Temperature

#### APPLICATION INFORMATION

The SSM2135 is a low voltage audio amplifier that has exceptionally low noise and excellent sonic quality even when driving loads as small as 25  $\Omega$ . Designed for single supply use, the SSM2135's inputs common-mode and output swing to zero volts. Thus with a supply voltage at +5 V, both the input and output will swing from 0 V to +4 V. Because of this, signal dynamic range can be optimized if the amplifier is biased to a +2 V reference rather than at half the supply voltage.

The SSM2135 is unity-gain stable, even when driving into a fair amount of capacitive load. Driving up to 500 pF does not cause any instability in the amplifier. However, overshoot in the frequency response increases slightly.

The SSM2135 makes an excellent output amplifier for +5 V only audio systems such as a multimedia workstation, a CD output amplifier, or an audio mixing system. The amplifier has large output swing even at this supply voltage because it is designed to swing to the negative rail. In addition, it easily drives load impedances as low as 25  $\Omega$  with low distortion.

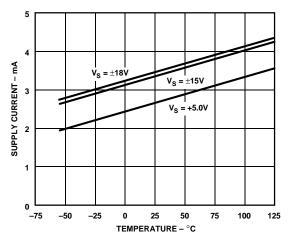

Figure 27. Supply Current vs. Temperature

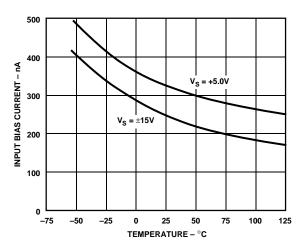

Figure 28. Input Bias Current vs. Temperature

The SSM2135 is fully protected from phase reversal for inputs going to the negative supply rail. However, an internal ESD protection diodes will turn "on" when either input is forced more than 0.5 V below the negative rail. Under this condition, input current in excess of 2 mA may cause erratic output behavior, in which case a current limiting resistor should be included in the offending input if phase integrity is required with excessive input voltages. A 500  $\Omega$  or higher series input resistor will prevent phase inversion even with the input pulled 1 volt below the negative supply.

"Hot" plugging the input to a signal generally does not present a problem for the SSM2135, assuming the signal does not have any voltage exceeding the device's supply voltage. If so, it is advisable to add a series input resistor to limit the current, as well as a Zener diode to clamp the input to a voltage no higher than the supply.

REV. D -7-

#### **APPLICATION CIRCUITS**

#### A Low Noise Stereo Headphone Driver Amplifier

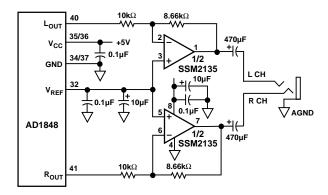

Figure 29 shows the SSM2135 used in a stereo headphone driver for multimedia applications with the AD1848, a 16-bit stereo codec. The SSM2135 is equally well suited for the serial-bused AD1849 stereo codec. The headphone's impedance can be as low as 25  $\Omega$ , which covers most commercially available high fidelity headphones. Although the amplifier can operate at up to  $\pm 18$  V supply, it is just as efficient powered by a single +5 V. At this voltage, the amplifier has sufficient output drive to deliver distortion-free sound to a low impedance headphone.

Figure 29. A Stereo Headphone Driver for Multimedia Sound Codec

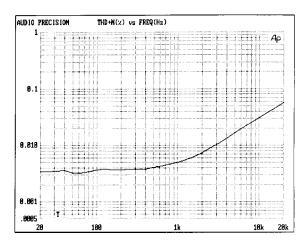

Figure 30 shows the total harmonic distortion characteristics versus frequency driving into a 32  $\Omega$  load, which is a very typical impedance for a high quality stereo headphone. The SSM2135 has excellent power supply rejection, and as a result, is tolerant of poorly regulated supplies. However, for best sonic quality, the power supply should be well regulated and heavily bypassed to minimize supply modulation under heavy loads. A minimum of  $10~\mu F$  bypass is recommended.

Figure 30. Headphone Driver THD+N vs. Frequency into a  $32 \Omega$  Load ( $V_S = +5 V$ , with 80 kHz Low-Pass Filter)

#### A Low Noise Microphone Preamplifier

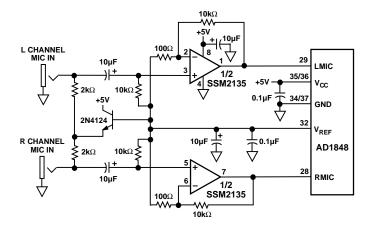

The SSM2135's 4.7 nV/ $\overline{\text{Hz}}$  input noise in conjunction with low distortion makes it an ideal device for amplifying low level signals such as those produced by microphones. Figure 31 illustrates a stereo microphone input circuit feeding a multimedia sound codec. As shown, the gain is set at 100 (40 dB), although it can be set to other gains depending on the microphone output levels. Figure 32 shows the preamplifier's harmonic distortion performance with 1 V rms output while operating from a single +5 V supply.

The SSM2135 is biased to 2.25 V by the  $V_{REF}$  pin of the AD1848 codec. The same voltage is buffered by the 2N4124 transistor to provide "phantom power" to the microphone. A typical electret condenser microphone with an impedance range of 100  $\Omega$  to 1 k $\Omega$  works well with the circuit. This power booster circuit may be omitted for dynamic microphone elements.

Figure 31. Low Noise Microphone Preamp for Multimedia Sound Codec

Figure 32. MIC Preamp THD+N Performance ( $V_S = +5 V$ ,  $A_V = 40 \text{ dB}$ ,  $V_{OUT} = 1 \text{ V rms}$ , with 80 kHz Low-Pass Filter)

-8- REV. D

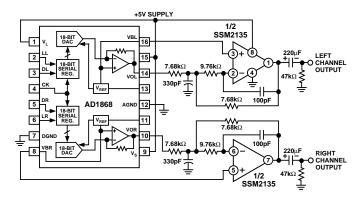

#### An 18-Bit Stereo CD-DAC Output Amplifier

The SSM2135 makes an ideal single supply stereo output amplifier for audio D/A converters because of its low noise and distortion. Figure 33 shows the implementation of an 18-bit stereo DAC channel. The output amplifier also provides low-pass filtering for smoothing the oversampled audio signal. The filter's cutoff frequency is set at 22.5 kHz and it has a maximally flat response from dc to  $20~\rm kHz$ .

As mentioned above, the amplifier's outputs can drive directly into a stereo headphone that has impedance as low as 25  $\Omega$  with no additional buffering required.

Figure 33. +5 V Stereo 18-Bit DAC

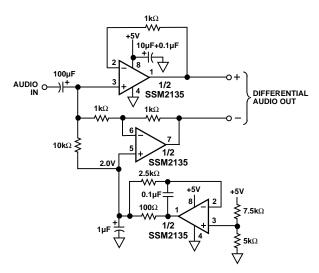

#### A Single Supply Differential Line Driver

Signal distribution and routing is often required in audio systems, particularly portable digital audio equipment for professional applications. Figure 34 shows a single supply line driver circuit that has differential output. The bottom amplifier provides a 2 V dc bias for the differential amplifier in order to maximize the output swing range. The amplifier can output a maximum of 0.8 V rms signal with a +5 V supply. It is capable of driving into 600  $\Omega$  line termination at a reduced output amplitude.

Figure 34. Single Supply Differential Line Driver

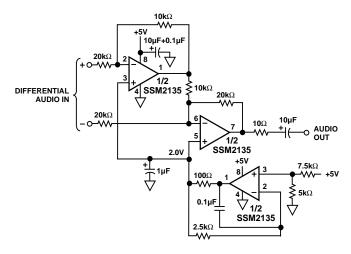

#### A Single Supply Differential Line Receiver

Receiving a differential signal with minimum distortion is achieved using the circuit in Figure 35. Unlike a difference amplifier (a subtractor), the circuit has a true balanced input impedance regardless of input drive levels. That is, each input always presents a 20 k $\Omega$  impedance to the source. For best common-mode rejection performance, all resistors around the differential amplifier must be very well matched. Best results can be achieved using a 10 k $\Omega$  precision resistor network.

Figure 35. Single Supply Balanced Differential Line Receiver

#### A Pseudo-Reference Voltage Generator

For single supply circuits, a reference voltage source is often required for biasing purposes or signal offsetting purposes. The circuit in Figure 36 provides a supply splitter function with low output impedance. The 1  $\mu F$  output capacitor serves as a charge reservoir to handle a sudden surge in demand by the load as well as providing a low ac impedance to it. The 0.1  $\mu F$  feedback capacitor compensates the amplifier in the presence of a heavy capacitive load, maintaining stability.

The output can source or sink up to 12 mA of current with +5~V supply, limited only by the  $100~\Omega$  output resistor. Reducing the resistance will increase the output current capability. Alternatively, increasing the supply voltage to 12 V also improves the output drive to more than 25 mA.

Figure 36. Pseudo-Reference Generator

REV. D \_9\_

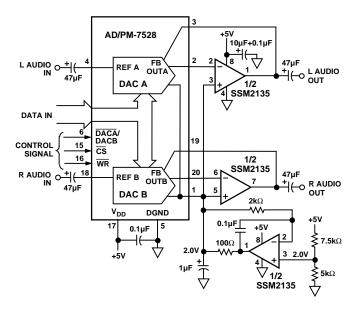

#### **A Digital Volume Control Circuit**

Working in conjunction with the AD7528/PM7528 dual 8-bit D/A converter, the SSM2135 makes for an efficient audio attenuator, as shown in Figure 37. The circuit works off a single +5 V supply. The DAC's are biased to a 2 V reference level which is sufficient to keep the DAC's internal R-2R ladder switches operating properly. This voltage is also the optimal midpoint of the SSM2135's common-mode and output swing range. With the circuit as shown, the maximum input and output swing is 1.25 V rms. Total harmonic distortion measures a respectable 0.01% at 1 kHz and 0.1% at 20 kHz. The frequency response at any attenuation level is flat to 20 kHz.

Each DAC can be controlled independently via the 8-bit parallel data bus. The attenuation level is linearly controlled by the binary weighting of the digital data input. Total attenuation ranges from 0 dB to 48 dB.

Figure 37. Digital Volume Control

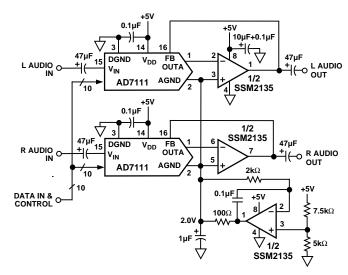

#### A Logarithmic Volume Control Circuit

Figure 38 shows a logarithmic version of the volume control function. Similar biasing is used. With an 8-bit bus, the AD7111 provides an 88.5 dB attenuation range. Each bit resolves a 0.375 dB attenuation. Refer to AD7111 data sheet for attenuation levels for each input code.

Figure 38. Single Supply Logarithmic Volume Control

–10– REV. D

```

* CMRR STAGE & POLE AT 6 kHZ

SPICE MACROMODEL

*SSM2135 SPICE Macro-Model

9/92, Rev. A

ECM

50

4

POLY(2) 3 60 2 60 0 1.6 1.6

JCB/ADI

CCM

50

51

26.5E-12

*Copyright 1993 by Analog Devices, Inc.

RCM1 50

51

1E6

RCM2 51

4

1

*Node Assignments

OUTPUT STAGE

Noninverting Input

R12 37 36 1E3

Inverting Input

R13 38 36 500

Positive Supply

C4 37 6

20E-12

Negative Supply

C5

38 39 20E-12

Output

M1 39 36 4 4 MN L=9E-6 W=1000E-6 AD=15E-9 AS=15E-9

M2 45 36 4 4 MN L=9E-6 W=1000E-6 AD=15E-9 AS=15E-9

.SUBCKT SSM2135

3

2

6

5

39 47 DX

D6 47 45 DX

* INPUT STAGE

Q3 39 40 41

QPA 8

R3

4

19

1.5E3

40 DC 0.861

VB

7

R4

4

20

1.5E3

R14 7

41 375

19

20

C1

5.311E-12

Q4 41 7

43

QNA 1

I1

7

18

106E-6

R17 7

43 15

2

IOS

3

25E-09

12

Q5 43 39 6

ONA 20

EOS

POLY(1)

25E-06 1

5

51 4

Q6 46 45 6

QPA 20

3

18

PNP1

Q1

19

20

12

18

PNP1

R18 46 4

15

Q2

3

Q7

36 46 4

QNA 1

CIN

2

3E-12

36 4 4 MN L=9E-6 W=2000E-6 AD=30E-9 AS=30E-9

D1

3

1

DY

2

D2

1

DY

* NONLINEAR MODELS USED

5

2

22

0

ΕN

1

GN1

0

2

25

0

1E-5

GN2

0

3

.MODEL DX D (IS=1E-15)

28

0

1E-5

.MODEL DY D (IS=1E-15 BV=7)

.MODEL PNP1 PNP (BF=220)

* VOLTAGE NOISE SOURCE WITH FLICKER NOISE

.MODEL DEN D(IS=1E-12 RS=1016 KF=3.278E-15 AF=1)

DN1 21

22

DEN

.MODEL DIN D(IS=1E-12 RS=100019 KF=4.173E-15 AF=1)

DN2

22

23

DEN

.MODEL QNA NPN(IS=1.19E-16 BF=253 VAF=193 VAR=15 RB=2.0E3

0

DC 2

VN1

21

+ IRB=7.73E-6 RBM=132.8 RE=4 RC=209 CJE=2.1E-13 VJE=0.573

VN2

0

23

DC 2

+ MJE =0.364 CJC=1.64E-13 VJC=0.534 MJC=0.5 CJS=1.37E-12

+ VJS=0.59 MJS=0.5 TF=0.43E-9 PTF=30)

* CURRENT NOISE SOURCE WITH FLICKER NOISE

.MODEL QPA PNP(IS=5.21E-17 BF=131 VAF=62 VAR=15 RB=1.52E3

DN3

24

25

DIN

+ IRB=1.67E 5-RBM=368.5 RE=6.31 RC=354.4 CJE=1.1E-13

DN4

25

26

DIN

+ VJE=0.745 MJE=0.33 CJC=2.37E-13 VJC=0.762 MJC=0.4

VN3

24

0

DC 2

+ CJS=7.11E-13 VJS=0.45 MJS=0.412 TF=1.0E-9 PTF=30)

VN4

0

26

DC 2

.MODEL MN NMOS(LEVEL=3 VTO=1.3 RS=0.3 RD=0.3 TOX=8.5E-8

+ LD=1.48E-6WD=1E-6 NSUB=1.53E16UO=650 DELTA= 10VMAX=2E5

* SECOND CURRENT NOISE SOURCE

+ XJ=1.75E-6 KAPPA=0.8 ETA=0.066 THETA=0.01TPG=1 CJ=2.9E-4

DN5

27

28

DIN

+ PB=0.837 MJ=0.407 CJSW=0.5E-9 MJSW=0.33)

29

DIN

DN6

28

0

DC 2

VN5

27

.ENDS SSM-2135

VN6

0

29

DC 2

* GAIN STAGE & DOMINANT POLE AT .2000E+01 HZ

G2

34

36

19

20 2.65E-04

R7

34

36

39E+06

V3

35

4

DC

6

D4

36

35

DX

VB2

34

1.6

* SUPPLY/2 GENERATOR

ISY

7

4

0.2E-3

R10

7

60

40E + 3

R11

60

4

40E + 3

C3

60

0

1E-9

```

REV. D –11–

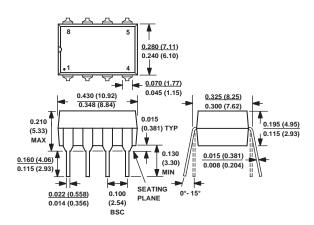

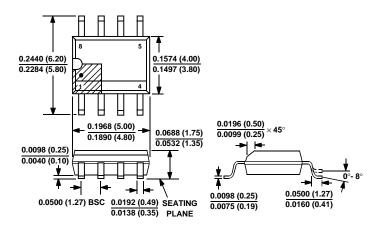

#### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

#### 8-Lead Plastic DIP (N-8)

#### 8-Lead Narrow-Body (SO-8)

Copyright © Each Manufacturing Company.

All Datasheets cannot be modified without permission.

This datasheet has been download from:

www.AllDataSheet.com

100% Free DataSheet Search Site.

Free Download.

No Register.

Fast Search System.

www.AllDataSheet.com